Incise has great team in Emulation and FPGA design have hands-on experience doing the following activities at several of our clients.

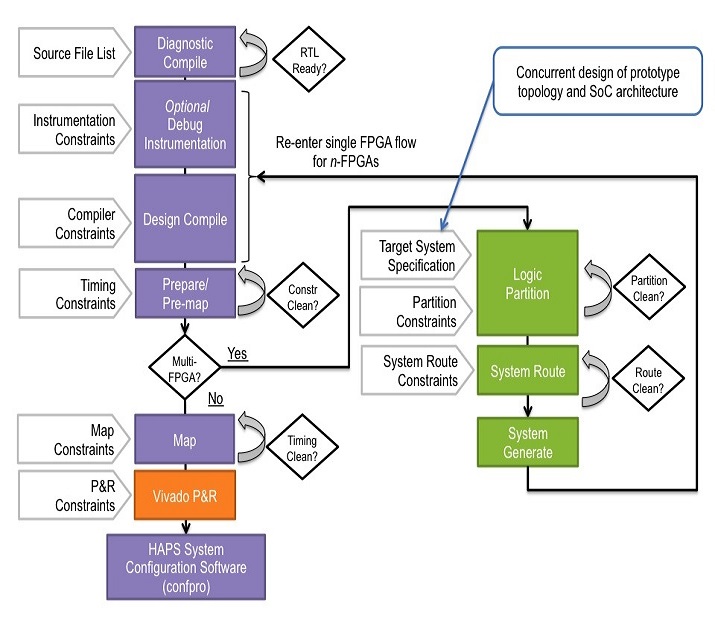

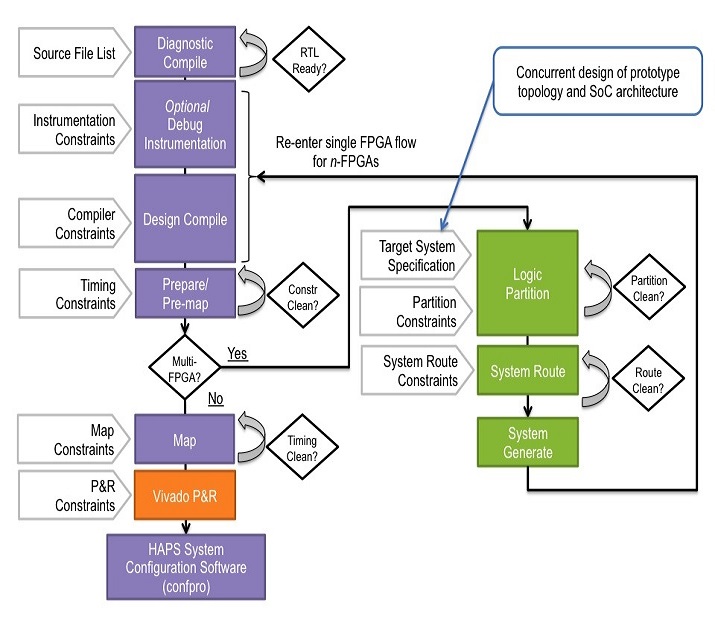

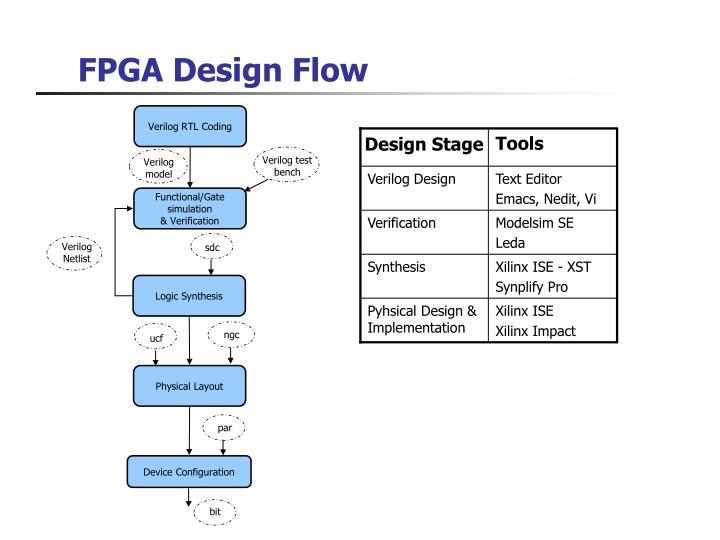

FPGA prototyping

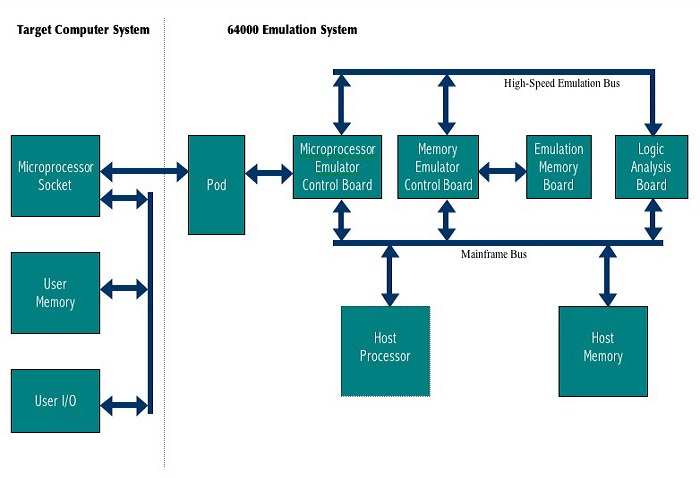

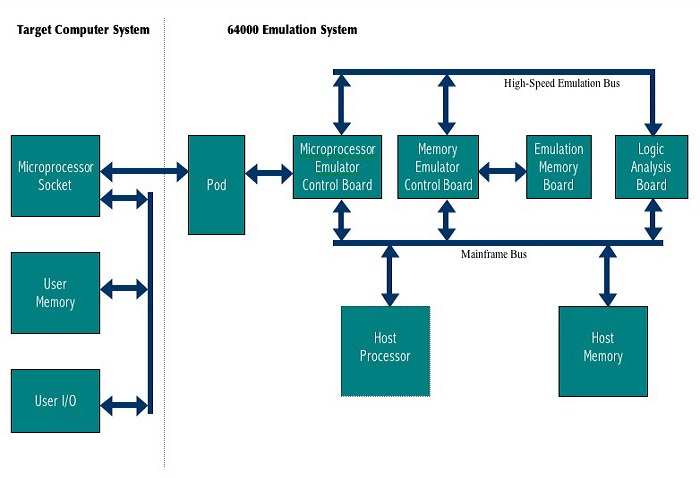

Processor based emulation

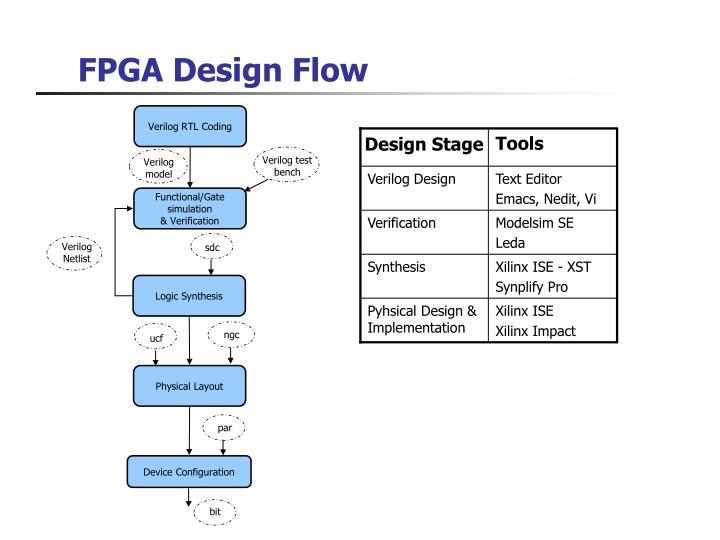

FPGA design

Incise has great team in Emulation and FPGA design have hands-on experience doing the following activities at several of our clients.