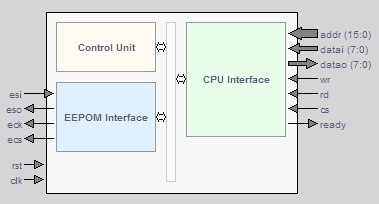

The DEEPROM performs communication and exchanges data between external serial EEPROM Memory and CPU’s RAM memory interface.

EEPROM Controller IP

Description

The DEEPROM performs communication and exchanges data between external serial EEPROM Memory and CPU’s RAM memory interface. Its contents are accessible to the CPU in the same manner as a common SRAM memory, but require READY input to expand the time access. Our proprietary core allows to map serial EEPROM in processor memory space and control it as the parallel memory. The controller automatically sends all control instructions and read /write memory locations. As for the CPU, the EEPROM is being connected to it through the DEEPROM. Moreover, it's visible and controlled as parallel SRAM with long access time. Our unique Core has been designed to operate with popular 25XXX SPI Serial EEPROMs (Atmel, Microchip).

Features

-

- Standard memory interface with ready control

- Configurable SPI parameters

- Serial clock prescaler

- SPI mode

- CS hold/setup

- Updating bits in EEPROM status register

- Simple interface allows easy connection to microcontrollers

- Fully synthesizable, static design with no internal tri-states

Applications

-

- Connection of Serial EEPROM to CPU

- Non-volatile data storing

Deliverables

- VHDL Source Code or/and VERILOG Source Code or/and Encrypted, or plain text EDIF

- VHDL & VERILOG test bench environment Active-HDL automatic simulation macros

- ModelSim automatic simulation macros Tests with reference responses

- Technical documentation Installation notes HDL core specification Datasheet

- Synthesis scripts Example application Technical support